Optimizing Remote Accesses for Offloaded Kernels Application to High-Level Synthesis for FPGA

#### Christophe Alias, Alain Darte, Alexandru Plesco

Compsys Team Laboratoire de l'Informatique du Parallélisme (LIP) École normale supérieure de Lyon

Workshop on Polyhedral Compilation Techniques (IMPACT'12) Jan. 23, 2012, Paris, France

Outline

HLS tools, interfaces, and communications Optimizing DDR accesses

- Context and motivations (see ASAP'10 paper)

HLS tools, interfaces, and communications

Optimizing DDR accesses

- 2 Communicating processes and "double buffering"

- 3 Kernel off-loading with polyhedral techniques

HLS tools, interfaces, and communications Optimizing DDR accesses

# High-level synthesis (HLS) tools

#### Many industrial and academic tools

• Spark, Gaut, Ugh, MMalpha, Catapult-C, Pico-Express, Impulse-C, etc.

#### Quite good at optimizing computation kernel

- Optimizes finite state machine (FSM).

- Exploits instruction-level parallelism (ILP).

- Performs operator selection, resource sharing, scheduling, etc.

But most designers prefer to ignore HLS tools and code in VHDL.

HLS tools, interfaces, and communications Optimizing DDR accesses

# High-level synthesis (HLS) tools

#### Many industrial and academic tools

• Spark, Gaut, Ugh, MMalpha, Catapult-C, Pico-Express, Impulse-C, etc.

#### Quite good at optimizing computation kernel

- Optimizes finite state machine (FSM).

- Exploits instruction-level parallelism (ILP).

- Performs operator selection, resource sharing, scheduling, etc.

But most designers prefer to ignore HLS tools and code in VHDL.

Still a huge problem for feeding the accelerators with data

- Lack of good interface support 🖝 write (expert) VHDL glue.

- Lack of communication opt. redesign the algorithm.

- Lack of powerful code analyzers 🖝 rename or find tricks.

HLS tools, interfaces, and communications Optimizing DDR accesses

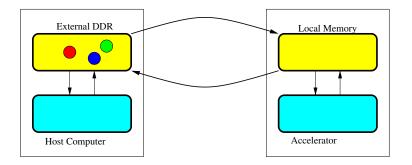

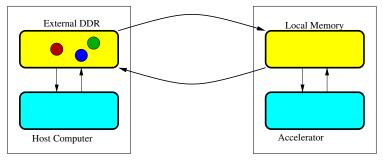

### Our goal: use HLS tools as back-end compilers

#### Focus on accelerators limited by bandwidth

- Use the adequate FPGA resources for computation throughput.

- Optimize bandwidth throughput.

HLS tools, interfaces, and communications Optimizing DDR accesses

イロト 不得下 イヨト イヨト 二日

4 / 25

## Our goal: use HLS tools as back-end compilers

#### Focus on accelerators limited by bandwidth

- Use the adequate FPGA resources for computation throughput.

- Optimize bandwidth throughput.

#### Apply source-to-source transformations

- Push the dirty work in the back-end compiler.

- Optimize transfers at C level.

- Compile any new functions with the same HLS tool.

HLS tools, interfaces, and communications Optimizing DDR accesses

## Our goal: use HLS tools as back-end compilers

#### Focus on accelerators limited by bandwidth

- Use the adequate FPGA resources for computation throughput.

- Optimize bandwidth throughput.

#### Apply source-to-source transformations

- Push the dirty work in the back-end compiler.

- Optimize transfers at C level.

- Compile any new functions with the same HLS tool.

#### Use Altera C2H as a back-end compiler. Main features:

- Syntax-directed translation to hardware.

- Basic DDR-latency-aware software pipelining with internal FIFOs.

- Full interface within the complete system.

- A few compilation pragmas.

HLS tools, interfaces, and communications Optimizing DDR accesses

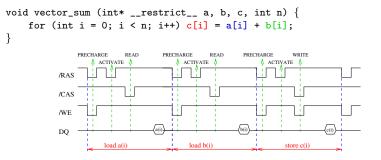

#### Asymmetric DDR accesses: need burst communications

Ex: DDR-400 128Mbx8, size 16MB, CAS 3, 200MHz. Successive reads to the same row every 10 ns, to different rows every 80 ns.

▶ bad spatial DDR locality can kill performances by a factor 8!

Non-optimized version: time gaps + data thrown away.

HLS tools, interfaces, and communications Optimizing DDR accesses

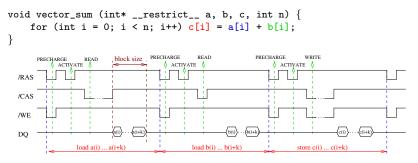

Asymmetric DDR accesses: need burst communications

Ex: DDR-400 128Mbx8, size 16MB, CAS 3, 200MHz. Successive reads to the same row every 10 ns, to different rows every 80 ns.

▶ bad spatial DDR locality can kill performances by a factor 8!

Optimized block version: reduces gaps, exploits burst.

HLS tools, interfaces, and communications Optimizing DDR accesses

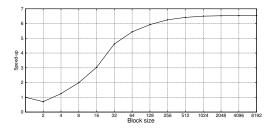

#### Experimental results: typical examples

Typical speed-up vs block size figure (here vector sum).

| Kernel | Speed-up | ALUT  | Dedicated | Total     | Total block | DSP block      | Max Frequency |

|--------|----------|-------|-----------|-----------|-------------|----------------|---------------|

|        |          |       | registers | registers | memory bits | 9-bit elements | (MHz > 100)   |

| SA     | 1        | 5105  | 3606      | 3738      | 66908       | 8              | 205.85        |

| VS0    | 1        | 5333  | 4607      | 4739      | 68956       | 8              | 189.04        |

| VS1    | 6.54     | 10345 | 10346     | 11478     | 269148      | 8              | 175.93        |

| MM0    | 1        | 6452  | 4557      | 4709      | 68956       | 40             | 191.09        |

| MM1    | 7.37     | 15255 | 15630     | 15762     | 335196      | 188            | 162.02        |

- SA: system alone.

- VS0 & VS1: vector sum direct & optimized version.

- MM0 & MM1: matrix-matrix multiply direct & optimized.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

# Outline

#### Context and motivations (see ASAP'10 paper)

- Communicating processes and "double buffering"

Loop tiling and the polytope model

Overview of the compilation scheme

Communication conjustion related work

- Communication coalescing: related work

- 3 Kernel off-loading with polyhedral techniques

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

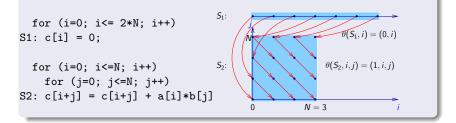

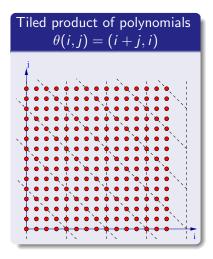

## Polyhedral model in a nutshell

#### Ex: product of polynomials

- Affine (parameterized) loop bounds and accesses

- Iteration domain, iteration vector

- Instance-wise analysis, affine transformations

- PIP: lexico-min in a polytope, given as a Quast (tree, internal node = affine inequality of parameters, leaf = affine function).

イロト イポト イヨト イヨト

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

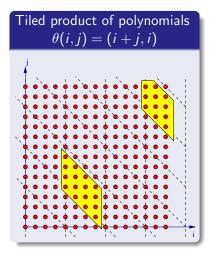

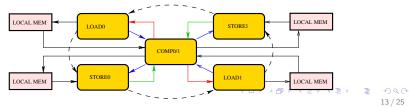

## Polyhedral model: tiling

- n loops transformed into n tile loops + n intra-tile loops.

- Expressed from permutable loops: affine function  $\theta$ , here  $\theta : (i,j) \mapsto (i+j,i)$ .

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

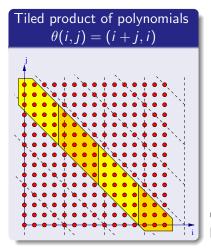

## Polyhedral model: tiling

- n loops transformed into n tile loops + n intra-tile loops.

- Expressed from permutable loops: affine function  $\theta$ , here  $\theta : (i,j) \mapsto (i+j,i)$ .

- Tile: atomic block operation.

- Increases granularity of computations.

- Enables communication coalescing (hoisting).

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

# Polyhedral model: tiling

- n loops transformed into n tile loops + n intra-tile loops.

- Expressed from permutable loops: affine function  $\theta$ , here  $\theta : (i,j) \mapsto (i+j,i)$ .

- Tile: atomic block operation.

- Increases granularity of computations.

- Enables communication coalescing (hoisting).

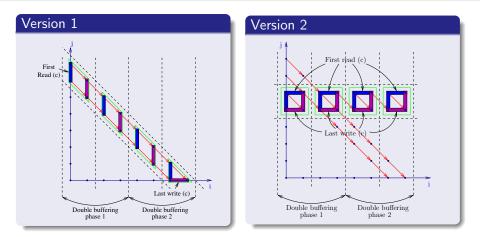

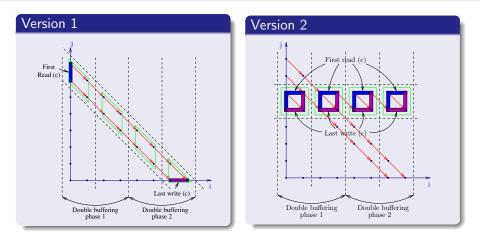

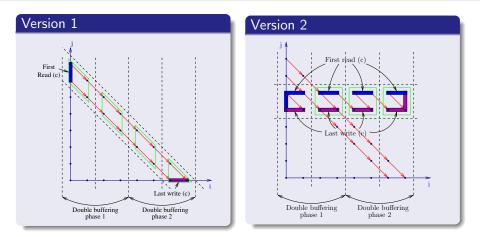

• We focus on a tile strip: double buffering  $\simeq$  loop unrolling by 2.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

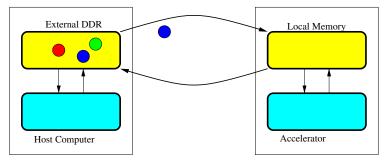

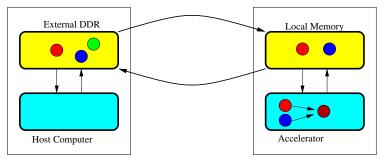

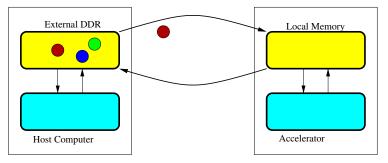

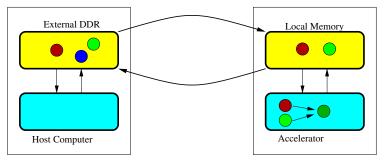

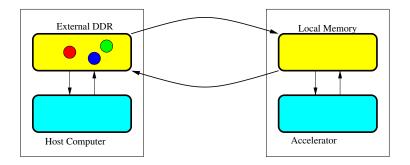

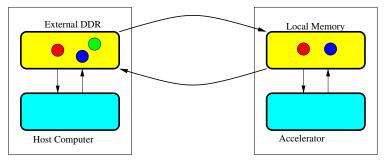

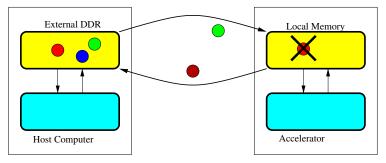

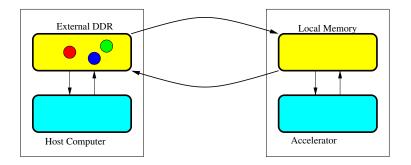

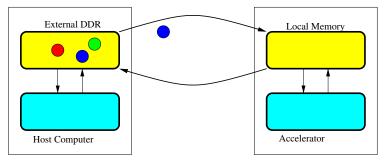

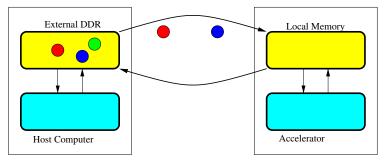

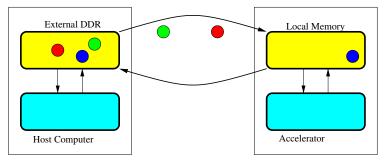

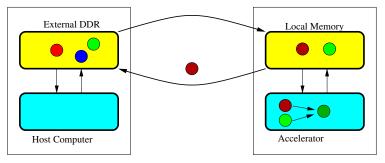

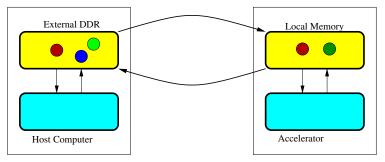

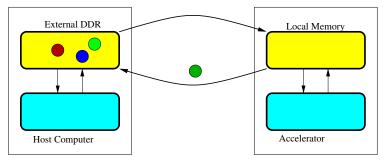

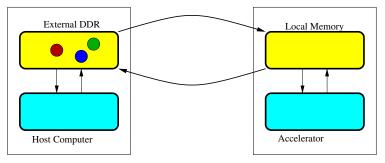

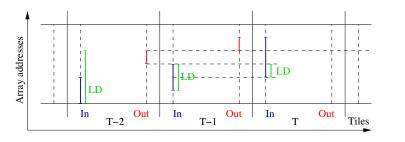

### Goals and principles: illustrating example

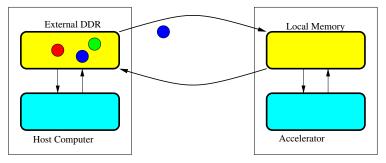

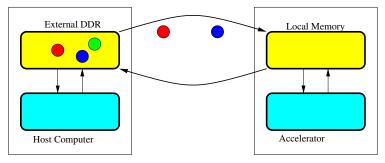

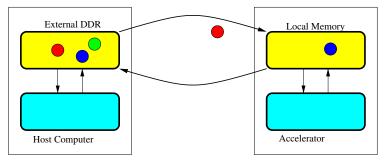

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 1: compute all tiles in sequence, with no overlap.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

#### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

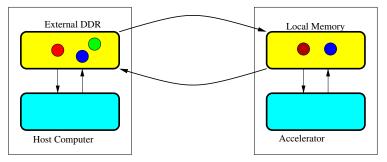

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 1: compute all tiles in sequence, with no overlap. Compute Tile 1 locally.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

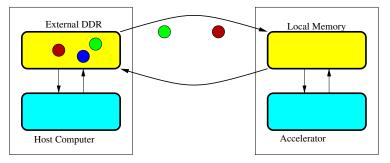

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 1: compute all tiles in sequence, with no overlap. Compute Tile 1 locally.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

#### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 1: compute all tiles in sequence, with no overlap. Bring results of Tile 1 to external DDR.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 1: compute all tiles in sequence, with no overlap. Bring results of Tile 1 to external DDR.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 1: compute all tiles in sequence, with no overlap. Compute Tile 2 locally.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 1: compute all tiles in sequence, with no overlap. Compute Tile 2 locally.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

#### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 1: compute all tiles in sequence, with no overlap. Bring results of Tile 2 to external DDR.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 1: compute all tiles in sequence, with no overlap. Bring results of Tile 2 to external DDR.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

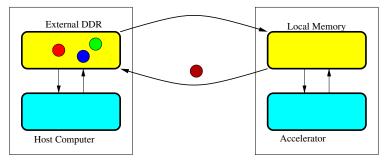

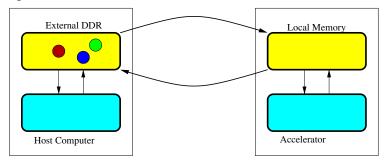

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

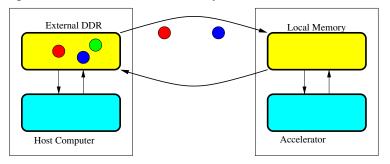

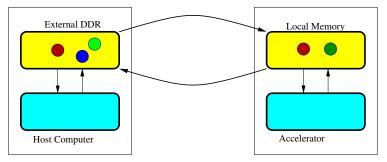

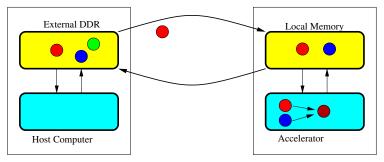

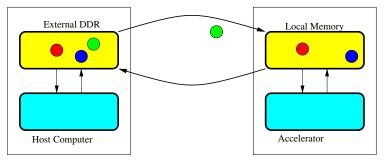

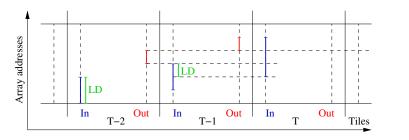

Approach 2: pipeline transfers & computations, no inter-tile reuse.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

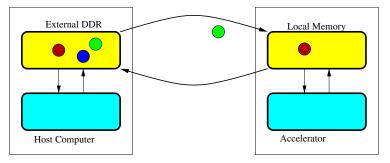

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 2: pipeline transfers & computations, no inter-tile reuse. Bring data for Tile 1 to local memory.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 2: pipeline transfers & computations, no inter-tile reuse. Bring data for Tile 1 to local memory.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

### Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 2: pipeline transfers & computations, no inter-tile reuse. Bring data for Tile 1 to local memory.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 2: pipeline transfers & computations, no inter-tile reuse. Bring data for Tile 1 to local memory.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

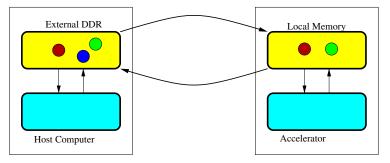

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 2: pipeline transfers & computations, no inter-tile reuse. Compute Tile 1 locally and start data transfer for Tile 2.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 2: pipeline transfers & computations, no inter-tile reuse. Compute Tile 1 locally and start data transfer for Tile 2.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 2: pipeline transfers & computations, no inter-tile reuse. Bring back results of Tile 1 and receive data for Tile 2.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

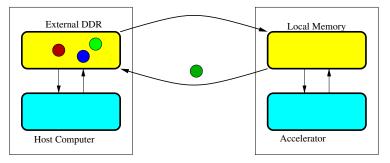

Approach 2: pipeline transfers & computations, no inter-tile reuse. Wrong for Tile 2: need inter-tile analysis + inter-tile reuse.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

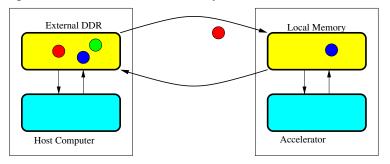

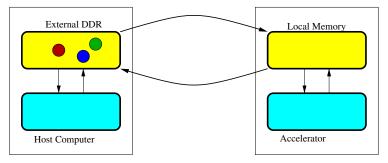

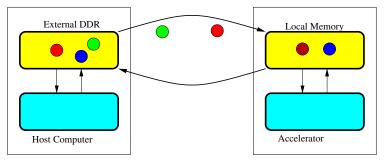

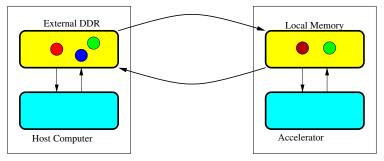

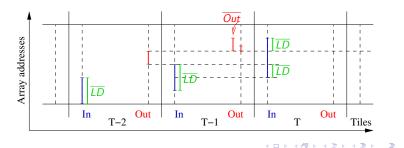

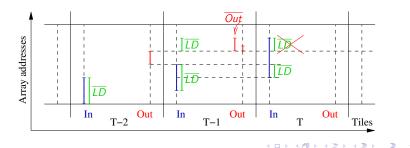

Approach 3: pipeline transfers/computations, use inter-tile reuse.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Bring data for Tile 1 to local memory.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Bring data for Tile 1 to local memory.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Bring data for Tile 1 to local memory, start transfer for Tile 2.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Bring data for Tile 1 to local memory, start transfer for Tile 2.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Compute Tile 1 locally and finish transfer for Tile 2.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Finish to compute Tile 1 locally.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

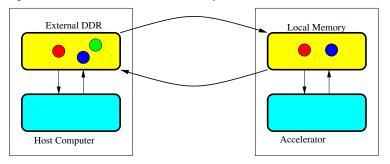

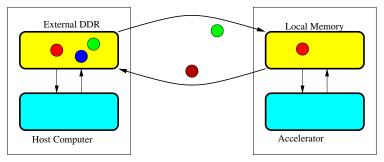

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Bring back results of Tile 1 and keep data to compute Tile 2.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Bring back results of Tile 1 and keep data to compute Tile 2.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Bring results of Tile 2 to external DDR.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Bring results of Tile 2 to external DDR.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Goals and principles: illustrating example

We use tiling to increase spatial locality in the DDR accesses. Here  $\bullet$  represents all elements of a given array for a given tile. Example: compute  $(\bullet, \bullet) \rightarrow \bullet$  followed by  $(\bullet, \bullet) \rightarrow \bullet$ .

Approach 3: pipeline transfers/computations, use inter-tile reuse. Bring results of Tile 2 to external DDR.

pipelining + data reuse reed for intra & inter-tile analysis + tile scheduling (software pipelining) + local memory management

10 / 25

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Loop tiling: impact on reuse and communication

**Load**  $\simeq$  first reads  $\cap$  tile domain **Store**  $\simeq$  last writes  $\cap$  tile domain.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Loop tiling: impact on reuse and communication

**Load**  $\simeq$  first reads  $\cap$  tile domain **Store**  $\simeq$  last writes  $\cap$  tile domain.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Loop tiling: impact on reuse and communication

**Load**  $\simeq$  first reads  $\cap$  tile domain **Store**  $\simeq$  last writes  $\cap$  tile domain.

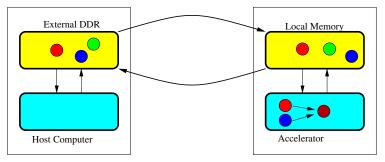

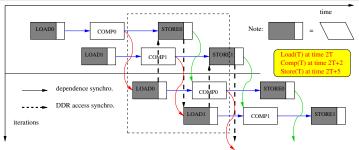

## Optimized transfers with maximal intra & inter-tile reuse

Double buffering style for optimized communications.

- Tiling + coarse-grain software pipelining = affine function  $\theta'$ .

- Communication coalescing: each tile T has a Load(T) and a Store(T).

- Transfers are done according to rows: spatial locality for DDR accesses.

- Exploits data reuse: temporal locality + fewer communications.

Local memory management defines local buffers with reuse.

- Requires lifetime analysis with respect to  $\theta'$ .

- Reduces memory size and provides access functions.

- We use lattice-based memory reduction:  $A\vec{i} \mod \vec{b}$  (mix between bounding box and sliding window).

Code generation generates final C code in a linearized form

- Placement of FIFO synchronizations.

- Boulet-Feautrier's method for polytope scanning.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

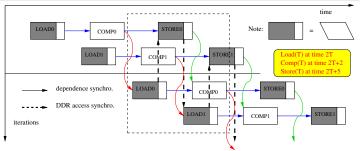

## Organization of communication & computation processes

- One function for each communicating process, one memory for each array.

- Dedicated FIFOs of size 1 for synchronizations.

- Transfers through explicit memory accesses.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

## Organization of communication & computation processes

- One function for each communicating process, one memory for each array.

- Dedicated FIFOs of size 1 for synchronizations.

- Transfers through explicit memory accesses.

## Related work: parallel languages & scratchpad memories

- Compiler-directed scratchpad memory hierarchy design & management: Kandemir, Choudhary, DAC'02.

- Effective communication coalescing for data-parallel applications: Chavarría-Miranda, Mellor-Crummey, PPoPP'05.

- Communication optimizations for fine-grained UPC applications: Chen, Iancu, Yelick, PACT'05.

- DRDU: A data reuse analysis technique for efficient scratchpad memory management: Issenin, Borckmeyer, Miranda, Dutt. ACM TODAES 2007.

- Automatic data movement and computation mapping for multi-level parallel architectures with explicitly managed memories: Baskaran, Bondhugula, Krishnam., Ramanujam, Rountev, Sadayappan, PPoPP'08.

- A mapping path for multi-GPGPU accelerated computers from a portable high level programming abstraction: Leung, Vasilache, Meister, Baskaran, Wohlford, Bastoul, Lethin, GPGPU'10.

- A reuse-aware prefetching scheme for scratchpad memory: Cong, Huang, Liu, Zou, DAC'11.

- PIPS is not (just) polyhedral software: Amini, Ancourt, Coelho, Creusillet, Guelton, Irigoin, Jouvelot, Keryell, Villalon, IMPACT'11.

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

# Main principles

```

for (i=0; i<N; i++)

for (j=0; j<N; j++)

S(i,j)

endfor

endfor

```

```

for (I=0; I<N; I+=b)

for (J=0; J<N; J+=b)

Transfer(I,J)

for (i=I; ifmin(I+b,N); i++)

for (j=J; j<min(J+b,N); j++)

S(i,j)

endfor

endfor

endfor

endfor</pre>

```

```

for (I=0; I<N; I+=b)

Transfer(I)

for (J=0; J<N; J+=b)

for (i=I; i<min(I+b,N); i++)

for (j=J; j<min(J+b,N); j++)

S(i,j)

endfor

endfor

endfor

endfor

endfor</pre>

```

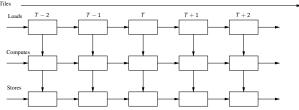

### Communication coalescing

- Hoist communications out of loops.

- Coalesce out of a tile or out of a tile strip.

## Static scratch-pad optimizations

- Decides statically which array portions will remain in SPM.

- Granularity of arrays and function calls.

## Dynamic scratch-pad optimizations

- Make a copy of distant memory before a tile or before a tile strip.

- Work at the granularity of array sections = approximation.

- Only "regular" inter-tile reuse (null space of affine functions or shifts).

- Apparently, no pipelining/overlapping (except in RStream).

Loop tiling and the polytope model Overview of the compilation scheme Communication coalescing: related work

# Main principles

```

for (i=0; i<N; i++)

for (j=0; j<N; j++)

S(i,j)

endfor

endfor

```

```

for (I=0; I<N; I+=b)

for (J=0; J<N; J+=b)

Transfer(I,J)

for (i=I; ifmin(I+b,N); i++)

for (j=J; j<min(J+b,N); j++)

S(i,j)

endfor

endfor

endfor

endfor</pre>

```

```

for (I=0; I<N; I+=b)

Transfer(I)

for (J=0; J<N; J+=b)

for (i=I; i<min(I+b,N); i++)

for (j=J; j<min(J+b,N); j++)

S(i,j)

endfor

endfor

endfor

endfor

endfor</pre>

```

### Communication coalescing

- Hoist communications out of loops.

- Coalesce out of a tile or out of a tile strip.

## Static scratch-pad optimizations

- Decides statically which array portions will remain in SPM.

- Granularity of arrays and function calls.

## Dynamic scratch-pad optimizations

- Make a copy of distant memory before a tile or before a tile strip.

- Work at the granularity of array sections = approximation.

- Only "regular" inter-tile reuse (null space of affine functions or shifts).

- Apparently, no pipelining/overlapping (except in RStream).

- ➡ But hypotheses and how "writes" are handled not clear.

Context and motivations (see ASAP'10 paper)

Optimizing reuse of remote accesses

Communicating processes and "double buffering"

Algorithmic solution based on parametric linear programming

Kernel off-loading with polyhedral techniques

Illustrating example

# Outline

- Context and motivations (see ASAP'10 paper)

- 2 Communicating processes and "double buffering"

- 8 Kernel off-loading with polyhedral techniques

- Optimizing reuse of remote accesses

- Algorithmic solution based on parametric linear programming

- Illustrating example

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

# What do we put in Load(T) and Store(T)?

### Minimal dependence structure:

#### Goal: make computations as local as possible.

- Reuse local data: intra and inter-tile reuse in a tile strip.

- Do not store in external memory after each write.

- Minimize live-ranges in local memory.

#### Two important consequences:

- Live-ranges can be all different: bounding box not enough.

- External memory not up-to-date: over-loading unsafe.

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

# General specification

### Define

- Load(T): data loaded from DDR just before executing tile T.

- Store(T): data stored to DDR just after T.

- In(T): data read before being written in the tile T.

- Out(T): data written by the tile T.

- $\overline{In}(T)$ : possibly read before being written, over-approximation of In(T).

- $\overline{\operatorname{Out}}(T)$ : data possibly written, over-approximation of  $\overline{\operatorname{Out}}(T)$ .

- $\underline{Out}(T)$ : data provably written, under-approximation of  $\underline{Out}(T)$ .

Can we give conditions for Load(T) and Store(T) to be valid? How to compute then? Can they be over-approximated too?

### Extreme solutions

- For all T, Load(T) = In(T),  $Store(T) = Out(T) \Rightarrow$  no inter-tile reuse.

- All Load(T) empty except first one

▶ no pipelining and overlapping.

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Formalization of valid, exact, and approximated load

### Valid load

$({\sf i})$  Load at least what is needed but not previously produced:

$$\operatorname{In}(\mathcal{T}) \setminus \operatorname{Out}(t < \mathcal{T}) \subseteq \operatorname{Load}(t \leq \mathcal{T})$$

(ii) Do not overwrite locally-defined data:

$\operatorname{Out}(t < T) \cap \operatorname{Load}(T) = \emptyset$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Formalization of valid, exact, and approximated load

#### Exact load

(i) Load exactly what is needed but not previously produced:

$$\cup_{t \leq T_{\mathsf{max}}} \left\{ \mathrm{In}(t) \setminus \mathrm{Out}(t' < t) \right\} = \mathrm{Load}(t \leq T_{\mathsf{max}})$$

(ii) All loads should be disjoint (no redundant transfers):

$\operatorname{Load}(T) \cap \operatorname{Load}(T') = \emptyset, \forall T \neq T'$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Formalization of valid, exact, and approximated load

Valid approximated load

(i) Load at least the exact amount of data:

$$\overline{\mathrm{In}}(\mathcal{T})\setminus \underline{\mathrm{Out}}(t<\mathcal{T})\subseteq \mathrm{Load}(t\leq\mathcal{T})$$

(ii) Do not overwrite possibly locally-defined data:

$\overline{\operatorname{Out}}(t < T) \cap \operatorname{Load}(T) = \emptyset$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Formalization of valid, exact, and approximated load

Valid approximated load

(i) Load at least the exact amount of data:

$$\overline{\mathrm{In}}(\mathcal{T})\setminus \underline{\mathrm{Out}}(t<\mathcal{T})\subseteq \mathrm{Load}(t\leq\mathcal{T})$$

(ii) Do not overwrite possibly locally-defined data:

$\overline{\operatorname{Out}}(t < T) \cap \operatorname{Load}(T) = \emptyset$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

# Subtleties due to writes and live-ranges

Main conclusions:

- If a data is locally written, be careful with data over-loading.

- If a data may be locally written, be careful when over-loading and when over-writing back to the DDR.

- Many schemes are possible: to minimize live-ranges, load as late as possible and store back as soon as possible.

- To avoid the problems due to over-loading and over-writing, two solutions:

- Design an exact scheme.

- Deal with approximations thanks to pre-loading.

- Live-range splitting (i.e., re-loads) may be useful. This has still to be explored.

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Handling approximations of data accesses

#### Exact situation

$\begin{aligned} &\operatorname{Store}(\mathcal{T}) = \operatorname{Out}(\mathcal{T}) \setminus \operatorname{Out}(t > \mathcal{T}) = \operatorname{LastWrite} \cap \mathcal{T} \\ &\operatorname{Load}(\mathcal{T}) = \operatorname{In}(\mathcal{T}) \setminus \{\operatorname{In}(t < \mathcal{T}) \cup \operatorname{Out}(t < \mathcal{T})\} = \operatorname{FirstReadBeforeWrite} \cap \mathcal{T} \end{aligned}$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

# Handling approximations of data accesses

#### Exact situation

$\begin{aligned} &\operatorname{Store}(\mathcal{T}) = \operatorname{Out}(\mathcal{T}) \setminus \operatorname{Out}(t > \mathcal{T}) = \operatorname{LastWrite} \cap \mathcal{T} \\ &\operatorname{Load}(\mathcal{T}) = \operatorname{In}(\mathcal{T}) \setminus \{\operatorname{In}(t < \mathcal{T}) \cup \operatorname{Out}(t < \mathcal{T})\} = \operatorname{FirstReadBeforeWrite} \cap \mathcal{T} \end{aligned}$

### Approximated situation

$\begin{array}{l} \operatorname{Store}(\mathcal{T}) = \overline{\operatorname{Out}}(\mathcal{T}) \setminus \overline{\operatorname{Out}}(t > \mathcal{T}) \\ \operatorname{Load}(\mathcal{T}) = \overline{\operatorname{In}}(\mathcal{T}) \setminus \left\{ \overline{\operatorname{In}}(t < \mathcal{T}) \cup \overline{\operatorname{Out}}(t < \mathcal{T}) \right\} \end{array}$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Handling approximations of data accesses

#### Exact situation

$\begin{aligned} &\operatorname{Store}(\mathcal{T}) = \operatorname{Out}(\mathcal{T}) \setminus \operatorname{Out}(t > \mathcal{T}) = \operatorname{LastWrite} \cap \mathcal{T} \\ &\operatorname{Load}(\mathcal{T}) = \operatorname{In}(\mathcal{T}) \setminus \{\operatorname{In}(t < \mathcal{T}) \cup \operatorname{Out}(t < \mathcal{T})\} = \operatorname{FirstReadBeforeWrite} \cap \mathcal{T} \end{aligned}$

#### Approximated situation NO!

Store(T) =  $\overline{\text{Out}}(T) \setminus \overline{\text{Out}}(t > T)$   $\bullet$  may write wrong values in DDR Load(T) =  $\overline{\text{In}}(T) \setminus \{\overline{\text{In}}(t < T) \cup \overline{\text{Out}}(t < T)\} \bullet$  may forget to load from DDR

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

#### Handling approximations of data accesses

#### Exact situation

$\begin{aligned} &\operatorname{Store}(\mathcal{T}) = \operatorname{Out}(\mathcal{T}) \setminus \operatorname{Out}(t > \mathcal{T}) = \operatorname{LastWrite} \cap \mathcal{T} \\ &\operatorname{Load}(\mathcal{T}) = \operatorname{In}(\mathcal{T}) \setminus \{\operatorname{In}(t < \mathcal{T}) \cup \operatorname{Out}(t < \mathcal{T})\} = \operatorname{FirstReadBeforeWrite} \cap \mathcal{T} \end{aligned}$

Possible solution with  $\overline{\operatorname{Out}}(T) \setminus \overline{\operatorname{Out}}(t > T) \subseteq \operatorname{Store}(T)$

$\begin{cases} \overline{\operatorname{In}}'(T) = \overline{\operatorname{In}}(T) \cup (\operatorname{Store}(T) \setminus \underline{\operatorname{Out}}(T)) & (\text{all data that are "read"}) \\ \overline{\operatorname{Ra}}(T) = \overline{\operatorname{In}}'(T) \setminus \underline{\operatorname{Out}}(t < T) & (\text{all data that need a remote access}) \\ \operatorname{Load}(T) = \left(\overline{\operatorname{In}}'(T) \cup (\overline{\operatorname{Out}}(T) \cap \overline{\operatorname{Ra}}(t > T))\right) \setminus \left(\overline{\operatorname{In}}'(t < T) \cup \overline{\operatorname{Out}}(t < T)\right) \end{cases}$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Handling approximations of data accesses

#### Exact situation

$\begin{aligned} &\operatorname{Store}(\mathcal{T}) = \operatorname{Out}(\mathcal{T}) \setminus \operatorname{Out}(t > \mathcal{T}) = \operatorname{LastWrite} \cap \mathcal{T} \\ &\operatorname{Load}(\mathcal{T}) = \operatorname{In}(\mathcal{T}) \setminus \{\operatorname{In}(t < \mathcal{T}) \cup \operatorname{Out}(t < \mathcal{T})\} = \operatorname{FirstReadBeforeWrite} \cap \mathcal{T} \end{aligned}$

Possible solution with  $\overline{\operatorname{Out}}(T) \setminus \overline{\operatorname{Out}}(t > T) \subseteq \operatorname{Store}(T)$

$\begin{cases} \overline{\mathrm{In}}'(\mathcal{T}) = \overline{\mathrm{In}}(\mathcal{T}) \cup (\mathrm{Store}(\mathcal{T}) \setminus \underline{\mathrm{Out}}(\mathcal{T})) & (\text{all data that are "read"}) \\ \overline{\mathrm{Ra}}(\mathcal{T}) = \overline{\mathrm{In}}'(\mathcal{T}) \setminus \underline{\mathrm{Out}}(t < \mathcal{T}) & (\text{all data that need a remote access}) \\ \mathrm{Load}(\mathcal{T}) = \left(\overline{\mathrm{In}}'(\mathcal{T}) \cup (\overline{\mathrm{Out}}(\mathcal{T}) \cap \overline{\mathrm{Ra}}(t > \mathcal{T}))\right) \setminus \left(\overline{\mathrm{In}}'(t < \mathcal{T}) \cup \overline{\mathrm{Out}}(t < \mathcal{T})\right) \end{cases}$

Intuitively, to reduce live-ranges, load ALAP and store ASAP.

- Store x just after T if x is never written after T, i.e.,  $x \notin \overline{\text{Out}}(t > T)$ .

- Preload x if x may be written, i.e.,  $x \in \overline{\text{Out}}(t \leq T_{\max}) \setminus \underline{\text{Out}}(t \leq T_{\max})$ .

- Load a value x always before it may be written, i.e.,  $x \notin \overline{Out}(t < T)$ .

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

イロト 不得下 イヨト イヨト 二日

#### Quast manipulations, simplifications, and inversions

For each array c, consider an array element  $c(\vec{m})$ .

- Compute 3 quasts, parameterized by  $\vec{m}$  and outer tile indices:

- $\overline{\operatorname{In}}(\vec{m}) = \min\{T \mid \vec{m} \in \overline{\operatorname{In}}(T)\}$  (Note:  $= +\infty$  if set empty).

- $\overline{\operatorname{Out}}(\vec{m}) = \min\{T \mid \vec{m} \in \overline{\operatorname{Out}}(T)\}.$

- $\underline{\operatorname{Out}}(\vec{m}) = \min\{T \mid \vec{m} \in \underline{\operatorname{Out}}(T)\}.$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

#### Quast manipulations, simplifications, and inversions

For each array c, consider an array element  $c(\vec{m})$ .

- Compute 3 quasts, parameterized by  $\vec{m}$  and outer tile indices:

- $\overline{\operatorname{In}}(\vec{m}) = \min\{T \mid \vec{m} \in \overline{\operatorname{In}}(T)\}$  (Note:  $= +\infty$  if set empty).

- $\overline{\operatorname{Out}}(\vec{m}) = \min\{T \mid \vec{m} \in \overline{\operatorname{Out}}(T)\}.$

- $\underline{\operatorname{Out}}(\vec{m}) = \min\{T \mid \vec{m} \in \underline{\operatorname{Out}}(T)\}.$

- Combine them to get T(m) = min(Out(m), min(Out(m), In(m))), with just a slight change: If min(Out(m), In(m)) = Out(m), replace by the leaf by -∞, i.e., no need to load. Then:

if  $T(\vec{m}) \neq \pm \infty$ , load  $\vec{m}$  just before tile  $T(\vec{m})$ .

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

#### Quast manipulations, simplifications, and inversions

For each array c, consider an array element  $c(\vec{m})$ .

- Compute 3 quasts, parameterized by  $\vec{m}$  and outer tile indices:

- $\overline{\operatorname{In}}(\vec{m}) = \min\{T \mid \vec{m} \in \overline{\operatorname{In}}(T)\}$  (Note:  $= +\infty$  if set empty).

- $\overline{\operatorname{Out}}(\vec{m}) = \min\{T \mid \vec{m} \in \overline{\operatorname{Out}}(T)\}.$

- $\underline{\operatorname{Out}}(\vec{m}) = \min\{T \mid \vec{m} \in \underline{\operatorname{Out}}(T)\}.$

- Combine them to get  $T(\vec{m}) = \min(\overline{\operatorname{Out}}(\vec{m}), \min(\underline{\operatorname{Out}}(\vec{m}), \overline{\operatorname{In}}(\vec{m})))$ , with just a slight change: If  $\min(\underline{\operatorname{Out}}(\vec{m}), \overline{\operatorname{In}}(\vec{m})) = \underline{\operatorname{Out}}(\vec{m})$ , replace by the leaf by  $-\infty$ , i.e., no need to load. Then: if  $T(\vec{m}) \neq \pm \infty$ , load  $\vec{m}$  just before tile  $T(\vec{m})$ .

- Invert T(m) into m(T) (m is now a variable, T a parameter), add the constraints for tile T, this gives Load(T) as a union of polytopes (or possibly LBLs) parameterized by tile indices.

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

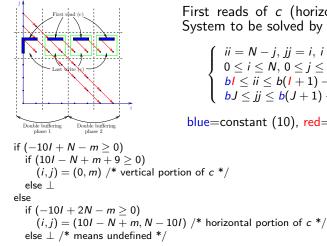

### Back to polynomial example

First reads of *c* (horizontal tiling). System to be solved by PIP:

$$\begin{array}{l} \begin{array}{l} (ii = N - j, jj = i, i + j = m) \\ 0 \leq i \leq N, \ 0 \leq j \leq N \\ bl \leq ii \leq b(l + 1) - 1 \\ bJ \leq jj \leq b(l + 1) - 1 \end{array}$$

blue=constant (10), red=parameter

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Back to polynomial example

First reads of *c* (horizontal tiling). System to be solved by PIP:

$$\begin{cases} ii = N - j, jj = i, i + j = m \\ 0 \le i \le N, 0 \le j \le N \\ bl \le ii \le b(l+1) - 1 \\ bJ \le jj \le b(J+1) - 1 \end{cases}$$

blue=constant (10), red=parameter

if  $(-10I + N - m \ge 0)$ if  $(10I - N + m + 9 \ge 0)$  /\* vertical band of elements, first tile \*/ (J, ii, jj, i, j) = (0, N - m, 0, 0, m)else  $\perp$  /\* means undefined \*/ else if  $(-10I + 2N - m \ge 0)$ if  $(-10I + N - m + 9 \ge 0)$  /\* horizontal band, first tile \*/ (J, ii, jj, i, j) = (0, 10I, 10I - N + m, 10I - N + m, N - 10I)else with  $k = \lfloor \frac{N+9m+9}{10} \rfloor$  /\* generic horizontal case \*/ (J, ii, jj, i, j) = (I + m - k, 10I, 10I - N + m, 10I - N + m, N - 10I)else  $\perp$  /\* undefined \*/

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Back to polynomial example

First reads of *c* (horizontal tiling). System to be solved by PIP:

$$\begin{array}{l} (ii = N - j, jj = i, i + j = m) \\ 0 \leq i \leq N, \ 0 \leq j \leq N \\ bl \leq ii \leq b(l + 1) - 1 \\ bJ \leq jj \leq b(l + 1) - 1 \end{array}$$

blue=constant (10), red=parameter

if  $(-10I + N - m \ge 0)$ if  $(10I - N + m + 9 \ge 0)$  /\* vertical band of elements, first tile \*/ (i,j) = (0,m)else  $\perp$ else if  $(-10I + 2N - m \ge 0)$ if  $(-10I + N - m + 9 \ge 0)$  /\* horizontal band, first tile \*/

$\begin{array}{l} (i,j) = (10I - N + m, N - 10I) \\ \text{else with } k = \lfloor \frac{N+9m+9}{10} \rfloor \ /* \text{ generic horizontal case } */\\ (i,j) = (10I - N + m, N - 10I) \\ \text{else } \perp \ /* \text{ means undefined } */ \end{array}$

23 / 25

Illustrating example

## Back to polynomial example

This gives the array elements whose first ac  $\{m \mid \max(0, N - 10I - 9) < m < N - 10I$

First reads of *c* (horizontal tiling). System to be solved by PIP:

$$\begin{cases} ii = N - j, jj = i, i + j = m \\ 0 \le i \le N, 0 \le j \le N \\ bl \le ii \le b(l+1) - 1 \\ bJ \le jj \le b(J+1) - 1 \end{cases}$$

blue=constant (10), red=parameter

cess is a read:

$$I \cup \{ m \mid N - 10I + 1 \le m \le 2N - 10I \}$$

$$( \Box ) \land ( \Box ) ( \Box ) \land ( \Box ) ( \Box ) \land ( \Box ) ( \Box ) ($$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

## Back to polynomial example

First reads of *c* (horizontal tiling). System to be solved by PIP:

$$\begin{cases} ii = N - j, jj = i, i + j = m \\ 0 \le i \le N, 0 \le j \le N \\ bl \le ii \le b(l+1) - 1 \\ bJ \le jj \le b(J+1) - 1 \end{cases}$$

blue=constant (10), red=parameter

$\{m \mid \max(0, N-10I-9) \le m \le N-10I\} \cup \{m \mid N-10I+1 \le m \le 2N-10I\}$

#### First operation that accesses m:

FirstOpRead $(m) = \{(i,j) \mid (i,j) = (0,m), \max(0, N - 10I - 9) \le m \le N - 10I\}$  $\cup \{(i,j) \mid (i,j) = (10I - N + m, N - 10I), N - 10I + 1 \le m \le 2N - 10I\}$

Introduce tile T and invert to get the data to be loaded at T:

FirstReadInTile(

$$T$$

) = { $m \mid \max(0, N - 10I - 9) \le m \le N - 10I, T = 0$ }

$\cup \{m \mid \max(1, 10T) \le m + 10I - N \le \min(N, 10T + 9)\}$

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

# Conclusion: contributions

- Bring HPC compilation tools to HLS of hardware accelerators.

- To our knowledge, first process to automate communications and integrate FPGA hardware accelerators, entirely at C level.

- Identifies important needs for synchronization mechanisms at source level and for better pragmas (e.g., *restrict* for pairs).

- Quite general analysis and transformations to pipeline kernel off-loading and optimize remote accesses (GPGPUs? Other?).

- Starting point for using HLS tools as back-end compilers.

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

#### Conclusion: perspectives

Many many opportunities for improvements.

- Design more efficient Quast simplifications, compare with ISL.

- Extend to parametric tile sizes.

- Implement approximations and live-range splitting.

- Explore link between coarse-grain schedule and memory size.

- Design more domain-specific code generation.

- Define compilation directives at C level for hardware synthesis.

- Include parallelism and multi-process accelerators

- Design customized memories and inter-processes buffers.

- Exploit schedule with slacks for GALS pipelined designs.

- Design a streaming language with shared memory for inter-process communication.

Optimizing reuse of remote accesses Algorithmic solution based on parametric linear programming Illustrating example

#### Conclusion: perspectives

Many many opportunities for improvements.

- Design more efficient Quast simplifications, compare with ISL.

- Extend to parametric tile sizes.

- Implement approximations and live-range splitting.

- Explore link between coarse-grain schedule and memory size.

- Design more domain-specific code generation.

- Define compilation directives at C level for hardware synthesis.

- Include parallelism and multi-process accelerators

- Design customized memories and inter-processes buffers.

- Exploit schedule with slacks for GALS pipelined designs.

- Design a streaming language with shared memory for inter-process communication.

25 / 25